#### 4-Bit DAC

Matthew Roberts

## Outline

- Abstract

- Schematic

- Output

- Simulation Plan and Results

- Layout

- Final Specifications

### Abstract

The objective is to design a device that will extract an analog signal given a series of digital codes with the proper time delay.

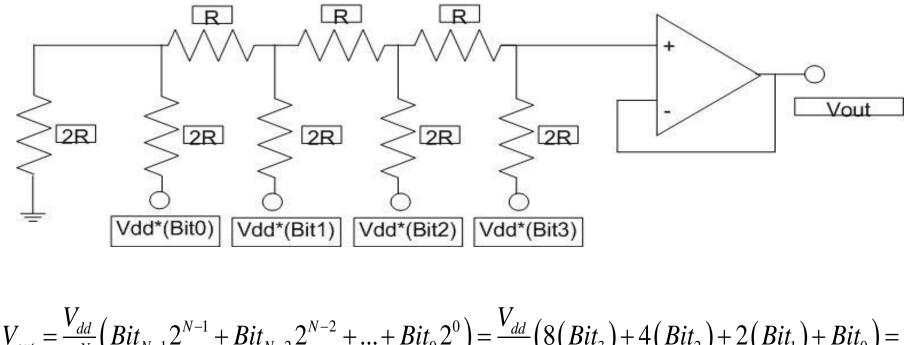

#### Schematic

$$V_{out} = \frac{1}{2^{N}} \left( Blt_{N-1}^{2} 2^{N} + Blt_{N-2}^{2} 2^{N} + ... + Blt_{0}^{2} 2^{N} \right) = \frac{1}{16} \left( 8 \left( Blt_{3}^{2} \right) + 4 \left( Blt_{2}^{2} \right) + 2 \left( Blt_{1}^{2} \right) + Blt_{0}^{2} \right) = \frac{1}{16} \left( 8 \left( Blt_{3}^{2} \right) + 4 \left( Blt_{2}^{2} \right) + 2 \left( Blt_{1}^{2} \right) + Blt_{0}^{2} \right) = \frac{1}{16} \left( 8 \left( Blt_{3}^{2} \right) + 4 \left( Blt_{2}^{2} \right) + 2 \left( Blt_{1}^{2} \right) + Blt_{0}^{2} \right) = \frac{1}{16} \left( 8 \left( Blt_{3}^{2} \right) + 4 \left( Blt_{2}^{2} \right) + 2 \left( Blt_{1}^{2} \right) + Blt_{0}^{2} \right) = \frac{1}{16} \left( 8 \left( Blt_{3}^{2} \right) + 4 \left( Blt_{2}^{2} \right) + 2 \left( Blt_{1}^{2} \right) + Blt_{0}^{2} \right) = \frac{1}{16} \left( 8 \left( Blt_{3}^{2} \right) + 4 \left( Blt_{2}^{2} \right) + 2 \left( Blt_{1}^{2} \right) + 2 \left( Blt_{1}^{2} \right) + Blt_{0}^{2} \right) = \frac{1}{16} \left( 8 \left( Blt_{3}^{2} \right) + 4 \left( Blt_{2}^{2} \right) + 2 \left( Blt_{1}^{2} \right) + Blt_{0}^{2} \right) = \frac{1}{16} \left( 8 \left( Blt_{3}^{2} \right) + 4 \left( Blt_{2}^{2} \right) + 2 \left( Blt_{1}^{2} \right) + 2 \left( Blt_{1}^{2$$

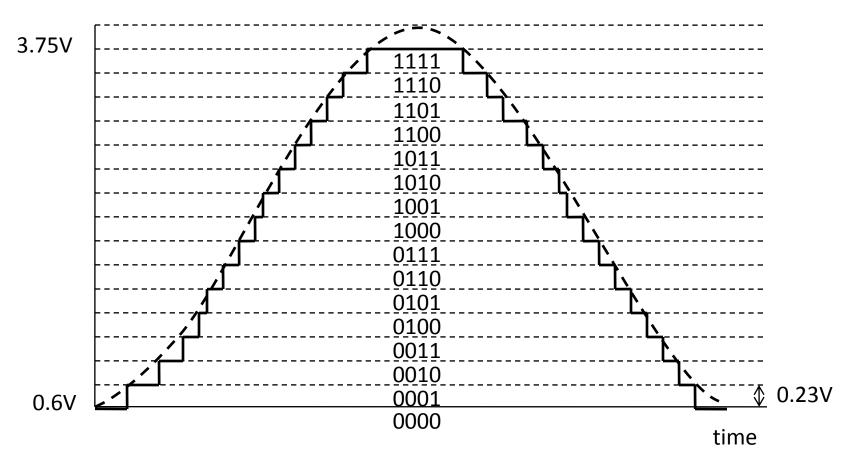

### Output

ΔV=Vmax/2^n=3.75/16=0.23V

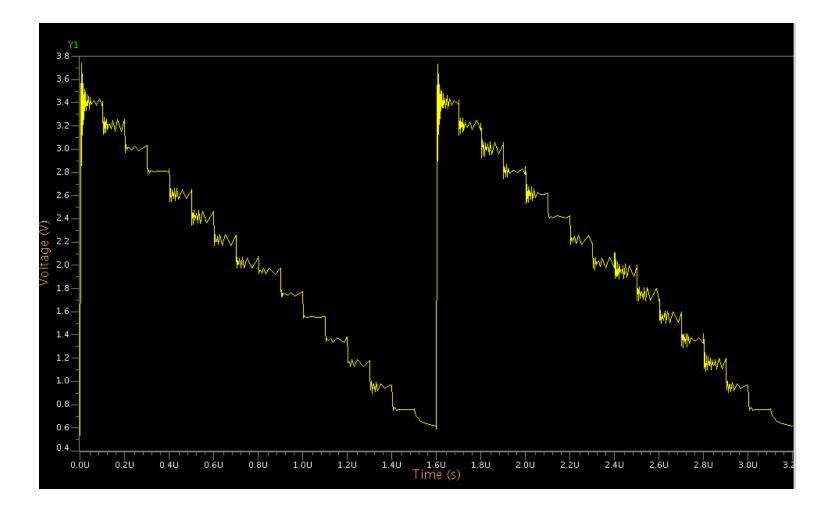

## **Simulation Plan**

- Test the linearity

- Use pulse sources on each input to run through all possible input combinations

- Generate an approximation of a ramp function.

#### **Simulation Results - Output**

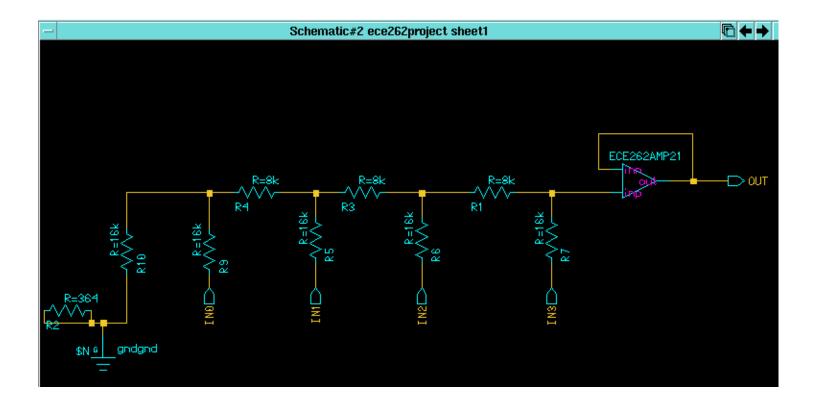

#### **Overall Schematic**

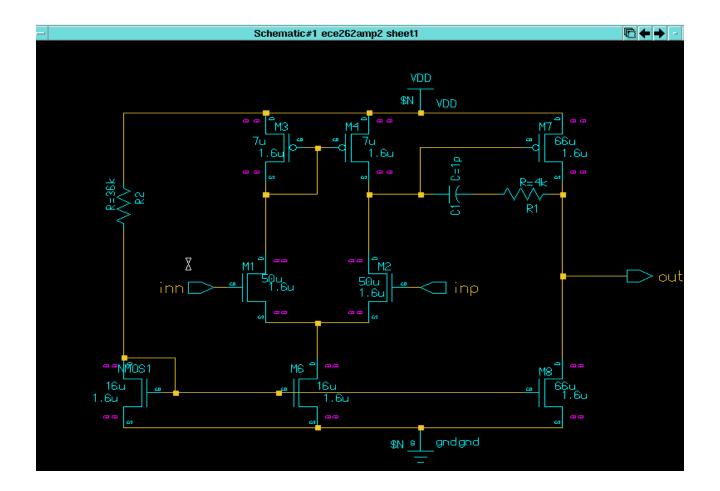

#### **Op-amp schematic**

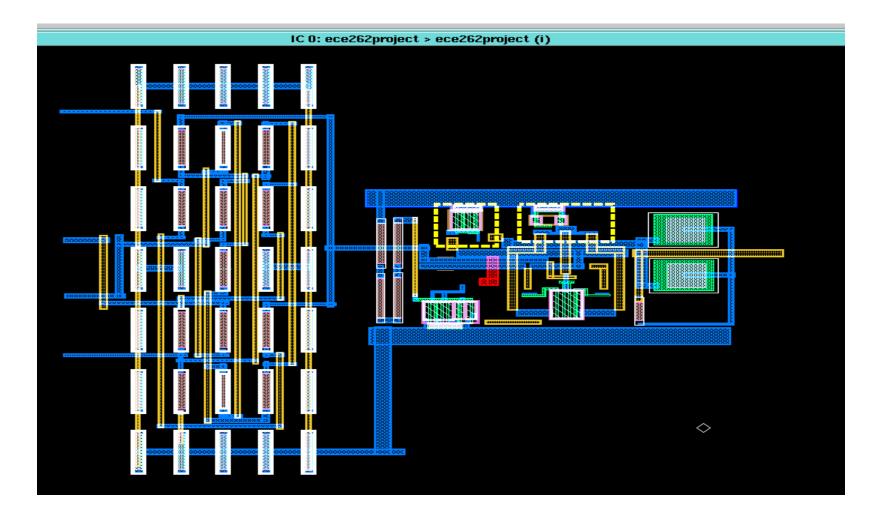

#### Layout

### **Final Specifications**

- Vdd = 5V

- Amplifier Power Dissipation = 5V\*0.6mA=3mW

- Resistor power dissipation (WC) (5V)^2/24kOhm=1mW

- Total Power Dissipation 4mW

- For the output stage: The following spec was met  $\Delta t < \frac{T_{\min}}{2^{N+1}}; \frac{\Delta V}{SR} = \frac{V_{dd}}{2^N SR} < \frac{1}{f_{\max} 2^{N+1}}; \frac{V_{dd}}{SR} < \frac{1}{2f_{\max}}; SR > 2V_{dd} f_{\max} = 2 \times 5V \times 100MHz$   $SR > 1\frac{mV}{ps}$

# Final Specifications (cont.)

- Components

- 5 resistors with resistance 2R

- 3 resistors with resistance R

- Op-amp

- 8 transistors

- 2 resistors

- 1 capacitor

- Unit Resistance (R) = 8kOhm

- 2R = 16kOhm

- Area of layout = 390um\*458um = 178,620(um)^2=0.18 (mm)^2

## **Design Challenges**

- The biggest design challenge was figuring out some LVS problems with device models.

- It was also a challenge to modify an existing op-amp layout to suit my purposes and to hook up a large number of resistors in a common-centroid layout.

- The rest of the design process went very smoothly