| Readings                         |                    |   |

|----------------------------------|--------------------|---|

| • P+H                            |                    |   |

| Chapter 4: Section 4.5           | 5-end of Chapter 4 |   |

|                                  |                    |   |

|                                  |                    |   |

|                                  |                    |   |

|                                  |                    |   |

|                                  |                    |   |

|                                  |                    |   |

|                                  |                    |   |

|                                  |                    |   |

| © 2011 Daniel J. Sorin from Roth | ECE 152            | 3 |

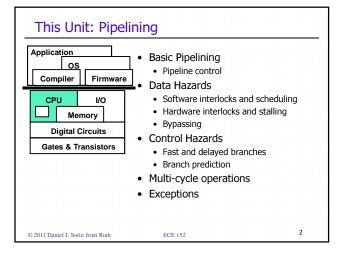

## Pipelining

- Important performance technique

- Improves insn throughput (rather than insn latency) • Laundry / SubWay analogy

- Basic idea: divide instruction's "work" into stages • When insn advances from stage 1 to 2

- Allow next insn to enter stage 1

- Etc.

- Key idea: each instruction does same amount of work as before

ECE 152

4

+ But insns enter and leave at a much faster rate

© 2009 Daniel J. Sorin from Roth

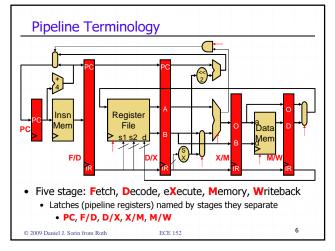

| Aside: Not All Pipelin                                                         | nes Have 5 Stages                                          |   |

|--------------------------------------------------------------------------------|------------------------------------------------------------|---|

| H&P textbook uses well-k                                                       | nown 5-stage pipe != all pipes                             |   |

| have 5 stages                                                                  |                                                            |   |

| <ul> <li>Some examples</li> </ul>                                              |                                                            |   |

| OpenRISC 1200: 4 stages                                                        |                                                            |   |

| <ul> <li>Sun UltraSPARC T1/T2 (Nia</li> </ul>                                  | igara/Niagara2): 6/8 stages                                |   |

| <ul> <li>AMD Athlon: 10 stages</li> </ul>                                      |                                                            |   |

| <ul> <li>Pentium 4: 20 stages</li> </ul>                                       |                                                            |   |

| <ul> <li>ICQ: why does Pentium 4</li> </ul>                                    | have so many stages?                                       |   |

| <ul> <li>ICQ: how can you possible<br/>into that many stages?</li> </ul>       | y break "work" to do single ins                            | n |

| <ul> <li>Moral of the story: in ECE<br/>pipe, but don't forget that</li> </ul> | 152, we focus on H&P 5-stage<br>t this is just one example | 2 |

| © 2009 Daniel J. Sorin from Roth                                               | ECE 152                                                    | 7 |