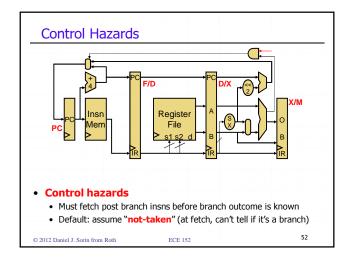

|      | rol hazards ind     |       |      |       |     | (01 | · no | t at | all | ) |  |

|------|---------------------|-------|------|-------|-----|-----|------|------|-----|---|--|

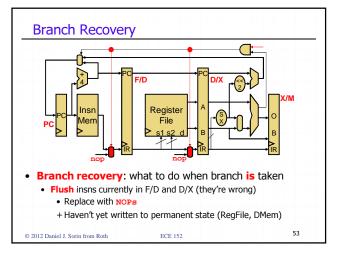

| • Pe | enalty for taken br | ranch | is 2 | 2 cyc | les |     |      |      |     |   |  |

|      |                     | 1     | 2    | 3     | 4   | 5   | 6    | 7    | 8   | 9 |  |

|      | addi \$3,\$0,1      | F     | D    | Х     | М   | W   |      |      |     |   |  |

|      | bnez \$3,targ       |       | F    | D     | Х   | М   | w    |      |     |   |  |

|      | sw \$6,4(\$7)       |       |      | с*    | с*  | F   | D    | Х    | М   | W |  |

|      |                     |       |      |       |     |     |      |      |     |   |  |

|      |                     |       |      |       |     |     |      |      |     |   |  |

|      |                     |       |      |       |     |     |      |      |     |   |  |

|      |                     |       |      |       |     |     |      |      |     |   |  |

|      |                     |       |      |       |     |     |      |      |     |   |  |

|      |                     |       |      |       |     |     |      |      |     |   |  |

|      |                     |       |      |       |     |     |      |      |     |   |  |

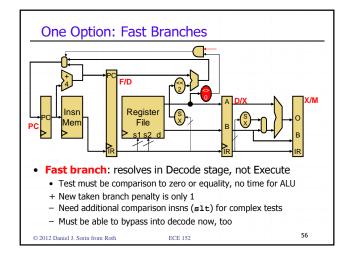

### Branch Performance

- Again, measure effect on CPI (clock period is fixed)

- Back of the envelope calculation

- Branch: 20%, load: 20%, store: 10%, other: 50%

- 75% of branches are taken (why so many taken?)

ECE 152

55

#### • CPI if no branches = 1

- CPI with branches = 1 + 0.20\*0.75\*2 = 1.3

- Branches cause 30% slowdown

- How do we reduce this penalty?

© 2012 Daniel J. Sorin from Roth

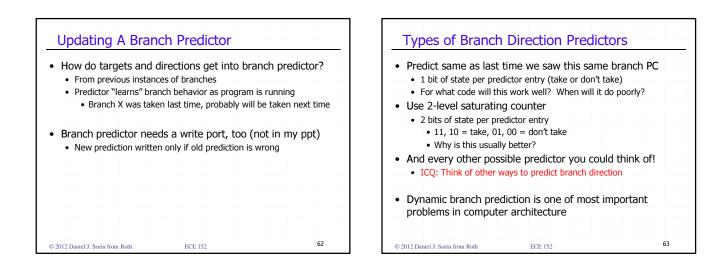

# Branch Prediction Performance

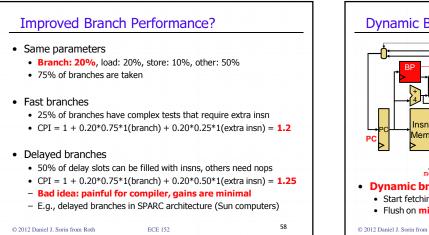

#### · Same parameters

• Branch: 20%, load: 20%, store: 10%, other: 50% • 75% of branches are taken

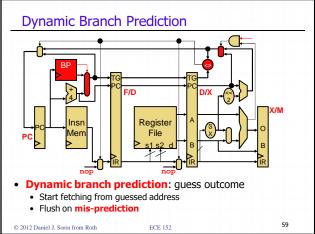

### • Dynamic branch prediction

- Assume branches predicted with 75% accuracy

- CPI = 1 + 0.20\*0.75\*2 = **1.15**

- Branch (esp. direction) prediction was a hot research topic Accuracies now 90-95%

ECE 152

### © 2012 Daniel J. Sorin from Roth

64

# **Pipelining And Exceptions** • Remember exceptions? - Pipelining makes them nasty • 5 instructions in pipeline at once Exception happens, how do you know which instruction caused it? ٠ Exceptions propagate along pipeline in latches Two exceptions happen, how do you know which one to take first? One belonging to oldest insn • When handling exception, have to flush younger insns • Piggy-back on branch mis-prediction machinery to do this • Just FYI – we'll solve this problem in ECE 252 65

ECE 152

© 2012 Daniel J. Sorin from Roth

| Pipeline Performance Summary                                               | Instruction-Level Parallelism (ILP)                                                                                                                 |  |  |  |  |  |  |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Base CPI is 1, but hazards increase it                                     | <ul> <li>Pipelining: a form of instruction-level parallelism (ILP)</li> <li>Parallel execution of insns from a single sequential program</li> </ul> |  |  |  |  |  |  |

| Remember: nothing magical about a 5 stage pipeline                         |                                                                                                                                                     |  |  |  |  |  |  |

| Pentium4 (first batch) had 20 stage pipeline                               | <ul> <li>There are ways to exploit ILP</li> </ul>                                                                                                   |  |  |  |  |  |  |

| Increasing <b>pipeline depth</b> (#stages)                                 | <ul> <li>We'll discuss this a bit more at end of semester, and then we'll<br/>really cover it in great depth in ECE 252</li> </ul>                  |  |  |  |  |  |  |

| + Reduces clock period (that's why companies do it)                        |                                                                                                                                                     |  |  |  |  |  |  |

| <ul> <li>But increases CPI</li> </ul>                                      | <ul> <li>We'll also talk a bit about thread-level parallelism (TLP)</li> </ul>                                                                      |  |  |  |  |  |  |

| Branch mis-prediction penalty becomes longer                               | and how it's exploited by multithreaded and multicore                                                                                               |  |  |  |  |  |  |

| <ul> <li>More stages between fetch and whenever branch computes</li> </ul> | processors                                                                                                                                          |  |  |  |  |  |  |

| Non-bypassed data hazard stalls become longer                              |                                                                                                                                                     |  |  |  |  |  |  |

| <ul> <li>More stages between register read and write</li> </ul>            |                                                                                                                                                     |  |  |  |  |  |  |

| At some point, CPI losses offset clock gains, question is when?            |                                                                                                                                                     |  |  |  |  |  |  |